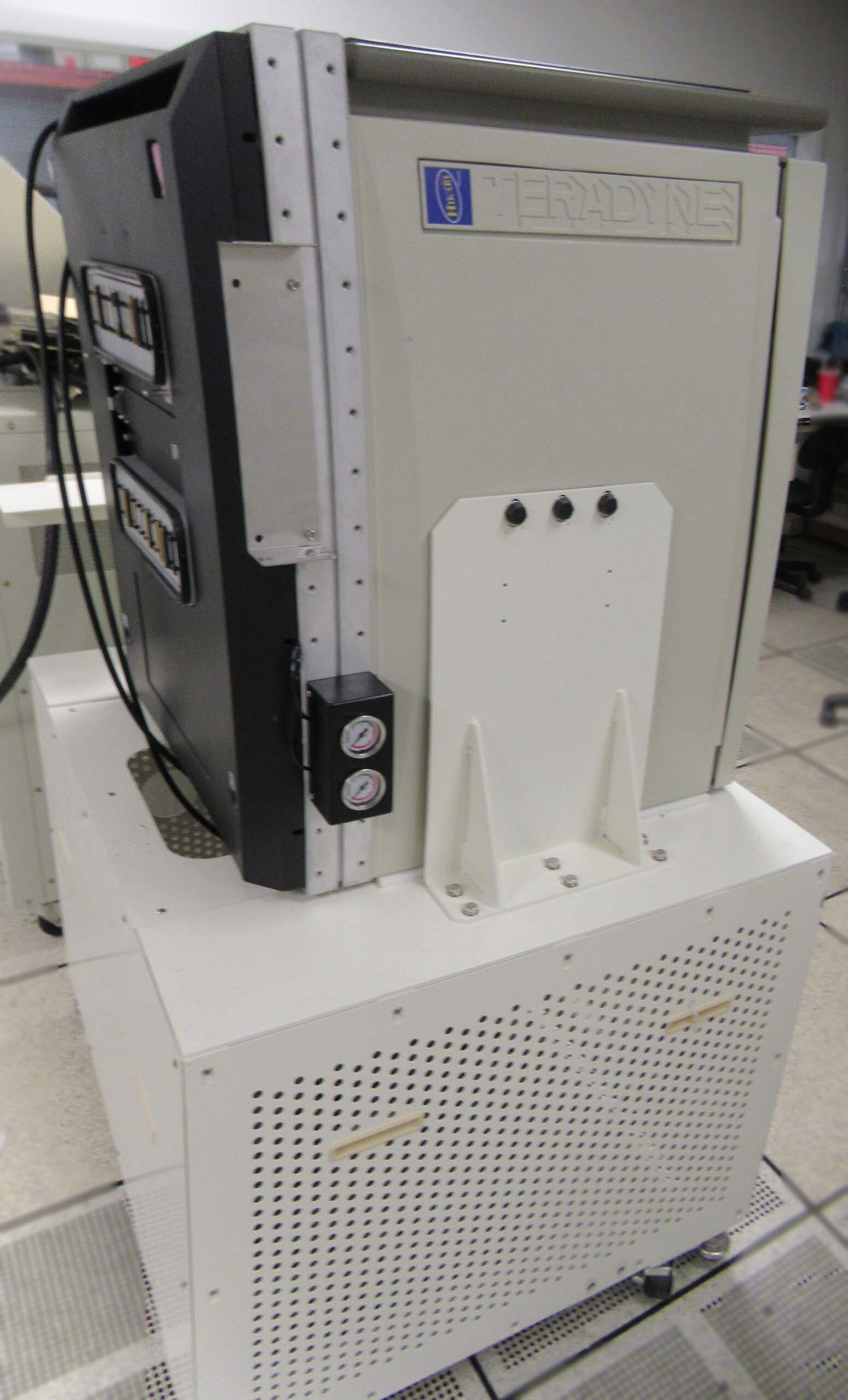

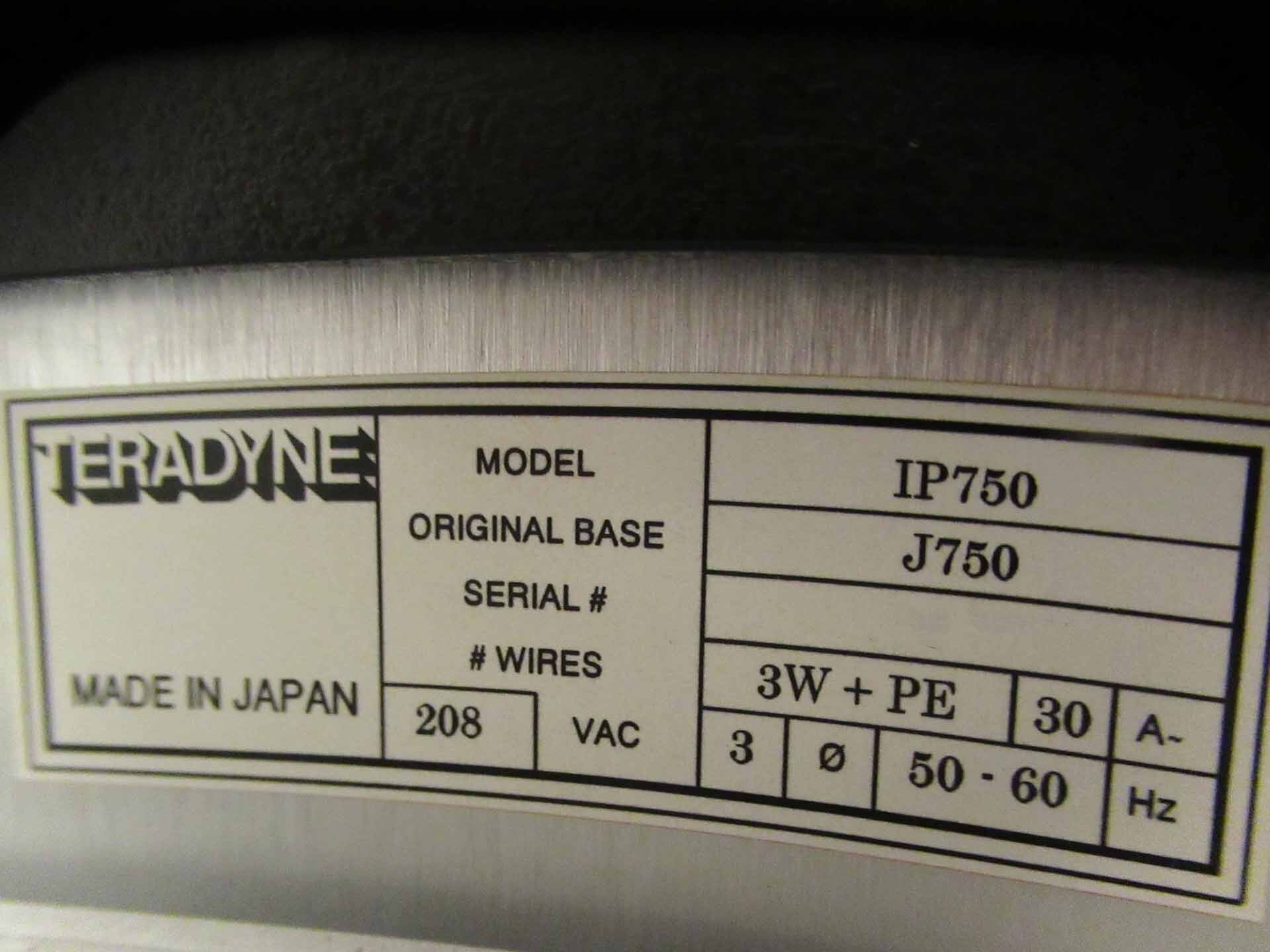

Used TERADYNE J750 #9411726 for sale

URL successfully copied!

Tap to zoom

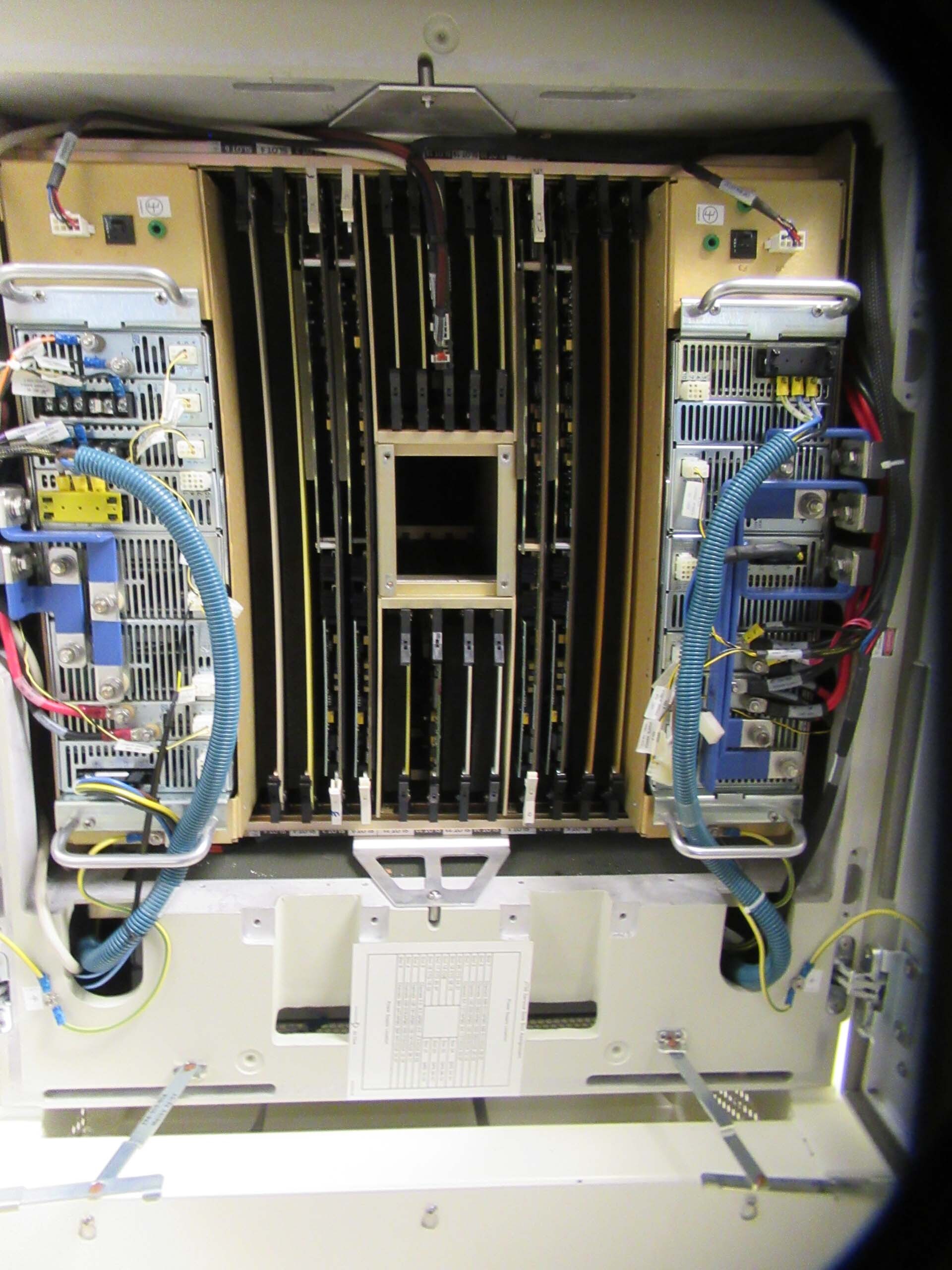

TERADYNE J750 Final Test Equipment is a mobile, high-capacity final test solution for testing a variety of today's complex system-on-chip (SoC) designs. With up to four tester heads, TERADYNE J 750 is capable of simulating mixed-signal test scenarios, allowing for improved silicon productivity across multiple segments. J750 features high-performance memory capable of testing multiple devices at once, reducing test time in mixed-signal environments. It also offers low power consumption for increased efficiency, as well as advanced data management tools for improved quality assurance and process control. The test unit utilizes a unique hardware-assisted test approach, achieving extremely short test time. This is enabled by a combination of speed, scalability, frequency, and memory capabilities in J 750 machine. The tool is configured with a high-speed, flexible ARM-based asset with variable-length vector logic, providing users with the scalability required to address both static and dynamic changes in the SoC testing requirements. The model also supports pin and clock-level testing, ensuring all device signals are properly tested. This includes high-speed and automatic vector generation, which allows for accurate testing of SoC devices prior to their release. Additionally, the equipment can accommodate up to four digital testers for increased accuracy during the testing process. In addition to its high-frequency and high-speed performance, TERADYNE J750 also supports advanced automation capabilities through its built-in high-speed data management tool. This allows for advanced data logging, trending, and reporting, to enable testers to monitor performance during the testing process. Furthermore, the system also has the flexibility to support specialty testing tools such as fault coverage analysis, power integrity analysis, and signal integrity analysis. TERADYNE J 750 is a powerful, high-capacity test unit designed to help manufacturers increase product yield and reduce test time while minimizing the impact of silicon technology advancements. It has been proven to reduce yield risks and provide reliable results throughout the machine-on-chip product life cycle. This makes it perfectly suited for today's high-hertz SoC testing needs.

There are no reviews yet